Fault Tree Analysis Diagrams

Fault Tree Analysis Diagrams

This solution extends ConceptDraw DIAGRAM.5 or later with templates, fault tree analysis example, samples and a library of vector design elements for drawing FTA diagrams (or negative analytical trees), cause and effect diagrams and fault tree diagrams.

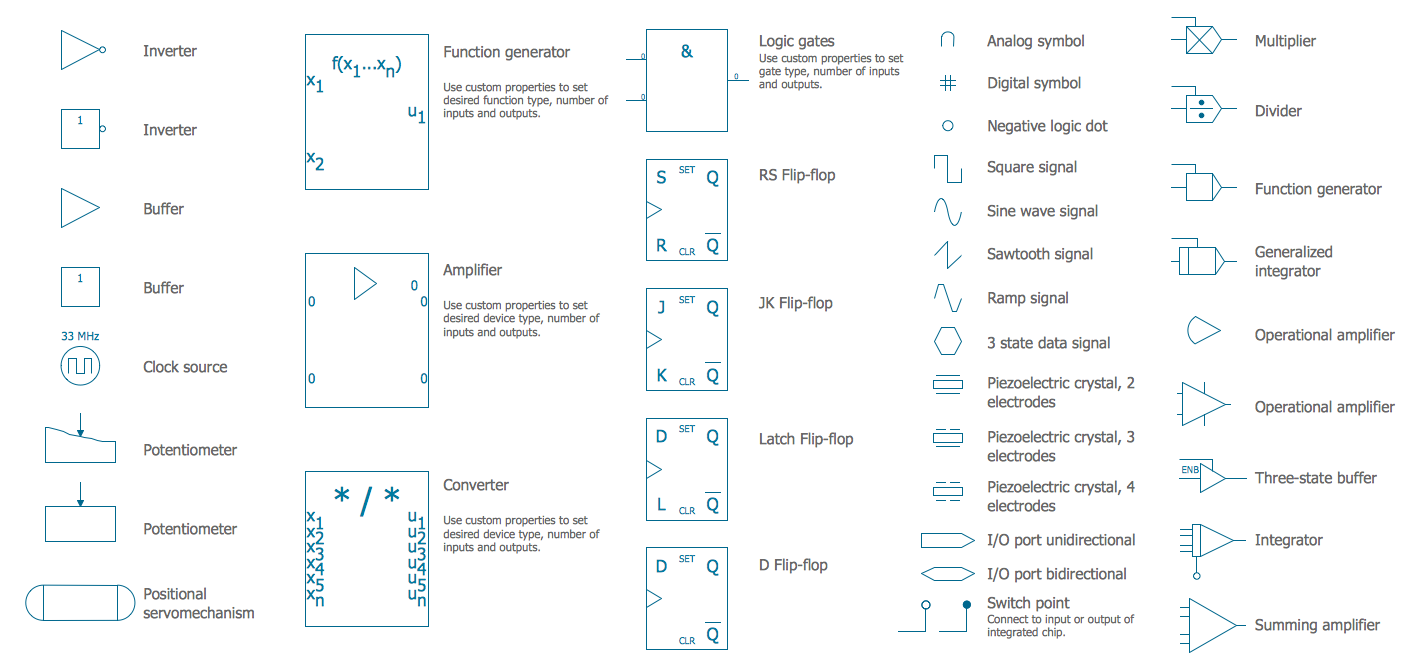

Electrical Symbols — Analog and Digital Logic

Digital electronics or digital (electronic) circuits are electronics that handle digital signals – discrete bands of analog levels – rather than by continuous ranges (as used in analogue electronics). All levels within a band of values represent the same numeric value. Because of this discretization, relatively small changes to the analog signal levels due to manufacturing tolerance, signal attenuation or parasitic noise do not leave the discrete envelope, and as a result are ignored by signal state sensing circuitry. 26 libraries of the Electrical Engineering Solution of ConceptDraw DIAGRAM make your electrical diagramming simple, efficient, and effective. You can simply and quickly drop the ready-to-use objects from libraries into your document to create the electrical diagram."A logic gate is an idealized or physical device implementing a Boolean function, that is, it performs a logical operation on one or more logical inputs, and produces a single logical output. Depending on the context, the term may refer to an ideal logic gate, one that has for instance zero rise time and unlimited fan-out, or it may refer to a non-ideal physical device...

Logic gates are primarily implemented using diodes or transistors acting as electronic switches, but can also be constructed using electromagnetic relays (relay logic), fluidic logic, pneumatic logic, optics, molecules, or even mechanical elements. With amplification, logic gates can be cascaded in the same way that Boolean functions can be composed, allowing the construction of a physical model of all of Boolean logic, and therefore, all of the algorithms and mathematics that can be described with Boolean logic.

Logic circuits include such devices as multiplexers, registers, arithmetic logic units (ALUs), and computer memory, all the way up through complete microprocessors, which may contain more than 100 million gates. In practice, the gates are made from field-effect transistors (FETs), particularly MOSFETs (metal–oxide–semiconductor field-effect transistors).

Compound logic gates AND-OR-Invert (AOI) and OR-AND-Invert (OAI) are often employed in circuit design because their construction using MOSFETs is simpler and more efficient than the sum of the individual gates.

In reversible logic, Toffoli gates are used." [Logic gate. Wikipedia]

The logic gate diagram template for the ConceptDraw PRO diagramming and vector drawing software is included in the Electrical Engineering solution from the Engineering area of ConceptDraw Solution Park.

Logic gates are primarily implemented using diodes or transistors acting as electronic switches, but can also be constructed using electromagnetic relays (relay logic), fluidic logic, pneumatic logic, optics, molecules, or even mechanical elements. With amplification, logic gates can be cascaded in the same way that Boolean functions can be composed, allowing the construction of a physical model of all of Boolean logic, and therefore, all of the algorithms and mathematics that can be described with Boolean logic.

Logic circuits include such devices as multiplexers, registers, arithmetic logic units (ALUs), and computer memory, all the way up through complete microprocessors, which may contain more than 100 million gates. In practice, the gates are made from field-effect transistors (FETs), particularly MOSFETs (metal–oxide–semiconductor field-effect transistors).

Compound logic gates AND-OR-Invert (AOI) and OR-AND-Invert (OAI) are often employed in circuit design because their construction using MOSFETs is simpler and more efficient than the sum of the individual gates.

In reversible logic, Toffoli gates are used." [Logic gate. Wikipedia]

The logic gate diagram template for the ConceptDraw PRO diagramming and vector drawing software is included in the Electrical Engineering solution from the Engineering area of ConceptDraw Solution Park.

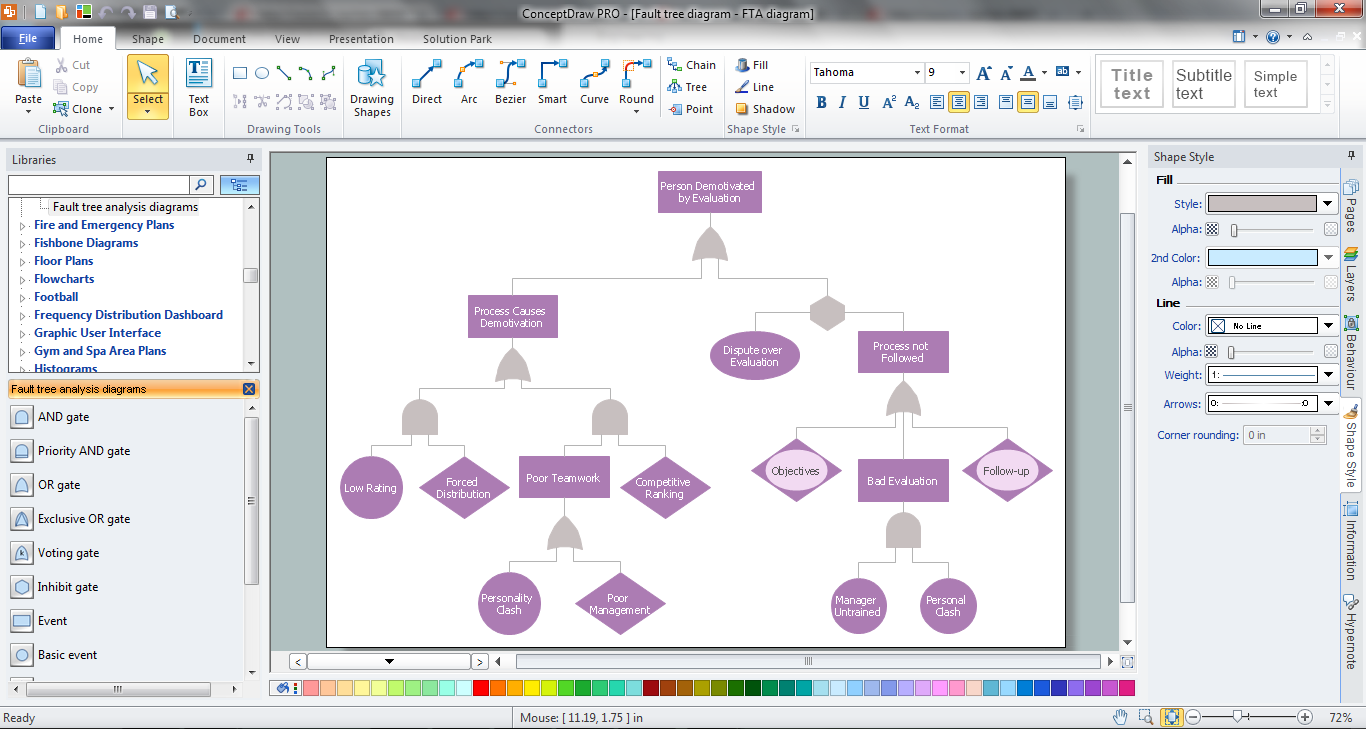

The vector stencils library "Fault tree analysis diagrams" contains 12 symbols for drawing Fault Tree Analysis (FTA) diagrams.

"Fault tree analysis (FTA) is a top down, deductive failure analysis in which an undesired state of a system is analyzed using Boolean logic to combine a series of lower-level events. This analysis method is mainly used in the fields of safety engineering and reliability engineering to understand how systems can fail, to identify the best ways to reduce risk or to determine (or get a feeling for) event rates of a safety accident or a particular system level (functional) failure. FTA is used in the aerospace, nuclear power, chemical and process, pharmaceutical, petrochemical and other high-hazard industries; but is also used in fields as diverse as risk factor identification relating to social service system failure.

In aerospace, the more general term "system Failure Condition" is used for the "undesired state" / Top event of the fault tree. These conditions are classified by the severity of their effects. The most severe conditions require the most extensive fault tree analysis. These "system Failure Conditions" and their classification are often previously determined in the functional Hazard analysis." [Fault tree analysis. Wikipedia]

The shapes example "Fault tree analysis diagrams" was created using the ConceptDraw PRO diagramming and vector drawing software extended with the Fault Tree Analysis Diagrams solution from the Engineering area of ConceptDraw Solution Park.

"Fault tree analysis (FTA) is a top down, deductive failure analysis in which an undesired state of a system is analyzed using Boolean logic to combine a series of lower-level events. This analysis method is mainly used in the fields of safety engineering and reliability engineering to understand how systems can fail, to identify the best ways to reduce risk or to determine (or get a feeling for) event rates of a safety accident or a particular system level (functional) failure. FTA is used in the aerospace, nuclear power, chemical and process, pharmaceutical, petrochemical and other high-hazard industries; but is also used in fields as diverse as risk factor identification relating to social service system failure.

In aerospace, the more general term "system Failure Condition" is used for the "undesired state" / Top event of the fault tree. These conditions are classified by the severity of their effects. The most severe conditions require the most extensive fault tree analysis. These "system Failure Conditions" and their classification are often previously determined in the functional Hazard analysis." [Fault tree analysis. Wikipedia]

The shapes example "Fault tree analysis diagrams" was created using the ConceptDraw PRO diagramming and vector drawing software extended with the Fault Tree Analysis Diagrams solution from the Engineering area of ConceptDraw Solution Park.

Fault Tree Analysis Software

ConceptDraw DIAGRAM extended with Fault Tree Analysis Diagrams Solution from the Industrial Engineering Area of ConceptDraw Solution Park is the best Fault Tree Analysis Software. First of all, Fault Tree Analysis Diagrams Solution provides a set of samples which are the good examples of easy drawing professional looking Fault Tree Analysis Diagrams.- Logic Gate Flowchart

- Logical network topology diagram | Network Diagram Software ...

- Logic gate diagram - Template | Engineering | Templates Logic Gates

- Logic gate diagram - Template | Electrical Symbols, Electrical ...

- Logic gate diagram - Template | Electrical Symbols — Logic Gate ...

- Logic gate diagram - Template | Circuits and Logic Diagram ...

- Logic gate diagram

- Electrical Symbols — Logic Gate Diagram

- Logic gate diagram - Template | Design elements - Logic gate ...

- 2-bit ALU - Logic gate diagram | How to Create a Fault Tree Analysis ...